《图灵完备》卡关记录1:锁存器

在学《计算机科学导论》的时候,Epi接触了门电路,但是那时候他没有过多在意

在学《离散数学》的时候,Epi狠狠吃了一记回旋镖,他决定使用真值表大法

在玩《图灵完备》时,Epi卡关了,警钟长鸣。

在《图灵完备》中,过了基础逻辑之后,游戏就会分为两条路,运算(ARITHMATIC)和存储(MEMORY),运算部分在了解了全加器,移位和补码的知识就很好过(暂时),但是存储的部分着实有些摸不着头脑,Epi依稀记得在计算机科学导论的课程里学习过SR锁存器,他决定复习一下

观前提示,本文中对所有元件输入节点的编号均从上到下记作输入A,B,C,D

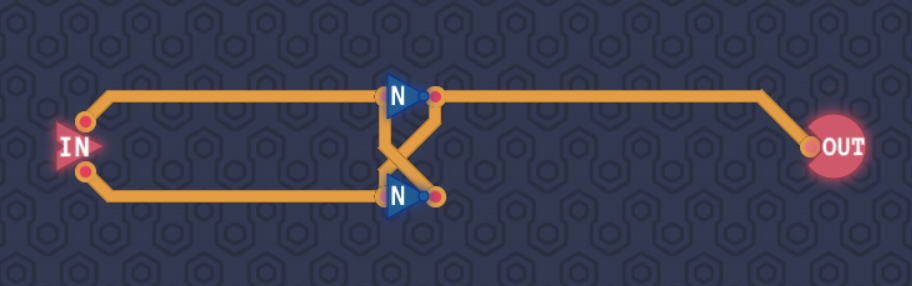

纠缠的门—SR锁存器

在SR锁存器中,在中间形成了一个“纠缠”的循环链,这个循环有两种进行状态

当输入IN的开关A开启时:循环以状态一运行,输出为0

当输入IN的开关B开启时:循环以状态二运行,输出为1

当输入开关都关闭时:输出由循环状态决定,可能是1,也可能是0

特别的,开关A,B都开启时,由于中间产生了冲突,最好不要这么做

总的来说,开关A 置0,开关B 置1,循环状态起到了存储信息的作用,这个装置就叫做SR锁存器

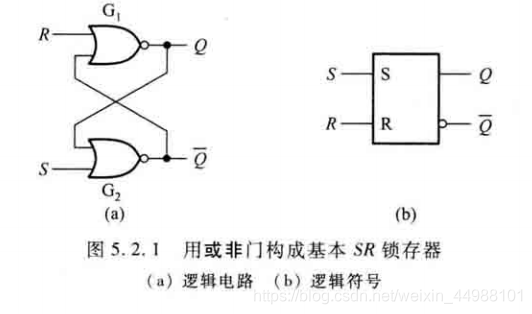

注:实际上SR锁存器使用或非门/与非门构建

下图展示了或非门构建的SR锁存器全输入1时,输出全为1,称为禁止态

S means Set(1), R means reset(0)

Flip-Flop触发器

看起来是跟锁存器类似的结构,不太懂(

D锁存器

但是,SR锁存器是由两个输入分别控制置0置1的,有些不好记不方便

Q: 能不能设计一个这样的电路:有两个输入,输入A控制是否启用锁存器,若输入A开启,则输入B为0时置0,输入1时置1,若输入A关闭,B不影响电路状态

可以的!电路如下(其中的FF为触发器,输入A为1时置0,输入B为1时置1)

这样我们就完成了D锁存器!

把这样的8个锁存器连接起来,就得到了寄存器~

顺带一提:发出文章的现在,epi卡在了Caculation这关